## Un convertisseur sigma-delta passif-actif bi-modes

Philippe Benabes, Sylvie Guessab

## ▶ To cite this version:

Philippe Benabes, Sylvie Guessab. Un convertisseur sigma-delta passif-actif bi-modes. 8ème Colloque sur le Traitement Analogique de l'Information, du Signal et ses applications, Oct 2007, Lyon, France. pp. 29-32. hal-00223007v2

# HAL Id: hal-00223007 https://centralesupelec.hal.science/hal-00223007v2

Submitted on 31 Jan 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Un convertisseur sigma-delta passif-actif bi-modes

Philippe BENABES

Département des signaux et systèmes

électroniques

SUPELEC

F91192 GIF/YVETTE, France

Sylvie GUESSAB

Département des signaux et systèmes

électroniques

SUPELEC

F91192 GIF/YVETTE, France

E-mail: philippe.benabes@supelec.fr, sylvie.guessab@supelec.fr

#### Résumé

Cet article présente un convertisseur analogique-numérique possédant deux modes de fonctionnement. Le premier mode se caractérise par une très faible consommation, associée à une faible résolution (9 bits). Dans le second mode, la résolution est accrue de 6 bits en théorie ; en contrepartie, la consommation augmente. En mode « faible consommation », le système est un convertisseur sigma-delta passif c'est-à-dire dont le modulateur utilise un filtre passe-bas passif, le seul élément actif étant le comparateur. En mode « haute résolution », le modulateur passif est positionné dans une boucle comprenant notamment un filtre passe-bas actif. Le principe de cette topologie bi-modes a été validé par des simulations au niveau fonctionnel et par le test d'un circuit prototype réalisé en technologie CMOS 0.35µm.

## 1. Introduction

Les modulateurs sigma-delta ( $\Sigma\Delta$ ) passifs permettent la réalisation de convertisseurs analogique-numérique de très faible consommation [1, 2]. Dans ces modulateurs, les filtres actifs habituellement utilisés dans les convertisseurs sigma-delta sont remplacés par des filtres passifs, le seul élément actif étant un comparateur.

L'avantage principal de ces convertisseurs est la très faible consommation de la partie analogique. En revanche, la bande passante et la résolution sont limitées. Pour ces raisons, les convertisseurs sigma-delta passifs sont surtout adaptés à la surveillance de signaux statiques, par exemple le niveau de tension d'une batterie dans un téléphone mobile. Il est à noter que le modulateur passif introduit une erreur de non-linéarité importante qui doit être corrigée numériquement, ce qui nécessite une calibration préalable.

Nous proposons ici un nouveau système de conversion utilisant un modulateur sigma-delta passif et capable de fonctionner selon deux modes. En mode « faible consommation » (dit « passif »), le modulateur est simplement suivi d'un filtre passe-bas numérique qui effectue également une décimation. La résolution attendue est d'environ 9 bits. En mode « haute résolution » (dit « actif »), le modulateur passif est positionné dans une boucle comprenant un filtre passe-bas actif et des fonctions

numériques. La résolution peut alors atteindre théoriquement 15 bits. Le mode actif peut par exemple être utilisé pour calibrer le modulateur sigma-delta passif.

Dans cet article, nous présentons tout d'abord le principe de cette topologie bi-modes ainsi que des résultats de simulation au niveau fonctionnel. Le circuit prototype réalisé pour valider le principe et déterminer les limitations est ensuite décrit. Enfin, les résultats de mesures sont confrontés à la théorie.

## 2. Architectures au niveau fonctionnel

#### 2.1 Le modulateur passif

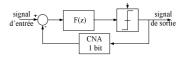

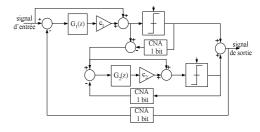

La conception d'un modulateur passif passe-bas à temps discret du deuxième ordre a été présentée dans un précédent article [3]. L'architecture est monoboucle (figure 1) et a été calculée à partir de l'architecture de type MSCL (Multi Stage Closed Loop [4]) présentée figure 2.

Figure 1. Modulateur sigma-delta à temps discret monoboucle

Figure 2. Modulateur sigma-delta d'ordre 2 de type MSCL

Les fonctions de transfert  $G_j(z)$  sont idéalement des intégrateurs. Compte tenu des défauts de réalisation, il s'agit généralement en pratique de filtres passe-bas actifs, que l'on peut exprimer en introduisant le coefficient  $Q_j$  ( $Q_j$  est l'inverse de la fréquence de coupure) :

$$G_{j}(z) = \frac{Q_{j}}{Q_{j} + 1} \frac{z^{-1}}{1 - \frac{Q_{j}}{Q_{j} + 1}} z^{-1}$$

(1)

On montre que la fonction de transfert vis-à-vis du bruit de l'architecture MSCL [3] est équivalente à celle d'une architecture monoboucle avec la fonction de transfert F(z) suivante :

$$F(z) = \prod_{j=1}^{j=ordre=2} (1 + c_j G_j(z)) - 1$$

(2)

Dans notre cas, le filtre de boucle est passif, le module de sa fonction de transfert n'excède donc pas 0 dB à la fréquence nulle. Nous ajustons donc la fonction de transfert de la formule (3) pour satisfaire cette contrainte et aboutissons à :

$$F(z) = \frac{\prod_{j=1}^{j=ordre=2} (1 + c_j \frac{Q_j}{Q_j + 1} \frac{z^{-1}}{1 - \frac{Q_j}{Q_j + 1} z^{-1}}) - 1}{\prod_{j=1}^{ordre=2} (1 + c_j Q_j) - 1}.$$

(3)

La formule (3) fait apparaître plusieurs degrés de liberté: les coefficients  $Q_j$  et  $c_j$ . Des simulations ont été effectuées afin de déterminer leur influence sur les performances du modulateur (résolution, stabilité) ainsi que sur le niveau de la tension d'entrée du comparateur. En effet, ce niveau est plus faible que dans un modulateur actif, il doit rester suffisant pour pouvoir être traité électroniquement. Les coefficients  $c_j$  peuvent être égaux entre eux, alors que les coefficients  $Q_j$  doivent être différents pour que le filtre soit réalisable avec uniquement des composants passifs. Compte tenu de ces contraintes, nous avons finalement retenu les valeurs suivantes:

$$c_1 = c_2 = 0.5, Q_1 = 10 \text{ et } Q_2 = 50$$

(4)

Avec ces valeurs, la résolution théorique pour un OSR de 100 est de l'ordre de 9 bits. L'entrée du comparateur est de l'ordre de 10 mV.

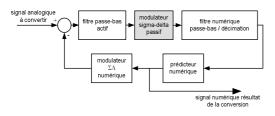

### 2.2 Principe de la topologie active

Le modulateur passif introduit une erreur de nonlinéarité importante lorsque le signal d'entrée s'écarte du point milieu de la plage de fonctionnement. Le principe des topologies actives est de placer le modulateur passif dans une boucle d'asservissement afin de maintenir son entrée autour du point milieu. Ce principe est illustré par l'architecture de la figure 3.

Figure 3. Topologie active simple

L'étage analogique du convertisseur se compose d'un filtre actif passe-bas et du modulateur passif. L'étage numérique se compose d'un filtre numérique passe-bas qui effectue également une décimation, d'un prédicteur et d'un modulateur sigma-delta numérique-analogique. Le

prédicteur donne une estimation du signal d'entrée à l'instant courant à partir des échantillons délivrés par le filtre numérique. Ce prédicteur peut être un simple intégrateur (avec un gain inférieur à 1 de manière à assurer la stabilité de la boucle). Après avoir été transformé par le modulateur sigma-delta numérique, le signal prédit est soustrait du signal d'entrée. Le filtre passe-bas en entrée élimine en partie le bruit introduit par le modulateur sigma-delta numérique.

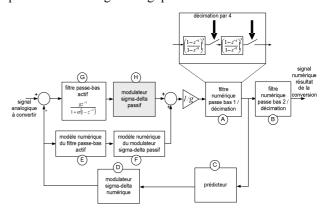

Le retard introduit par le filtre numérique augmente le temps de réponse de la boucle. Par conséquent, cette topologie n'est adaptée que pour des signaux lents. Afin d'obtenir un temps de réponse plus rapide, une autre topologie est proposée (figure 4). Le filtre numérique a été divisé en 2 étages. Le premier étage permet de réduire le bruit de quantification sans introduire un retard trop important. Les éléments (E) et (F) sont des modèles numériques de la partie analogique. Ils permettent d'augmenter la vitesse et la bande passante du convertisseur. Ils doivent être appariés aussi bien que possible avec l'étage analogique.

Figure 4. Topologie active rapide

## 3. Résultats de simulation à haut niveau

#### 3.1 Linéarité et résolution

Nous avons effectué dans un premier temps des simulations avec une entrée continue de manière à évaluer la linéarité et la résolution du convertisseur. Deux configurations ont été comparées :

- en mode passif: le modulateur passif seul suivi des filtres numériques 1 and 2 (A et B sur la figure 4);

- en mode actif : le gain du filtre actif d'entrée (g) est choisi égal à 8 et sa fréquence de coupure à  $f_e/40$  ( $f_e$  fréquence d'échantillonnage). Les éléments E et F sont supposés parfaitement appariés au modulateur passif. Le prédicteur C est un interpolateur linéaire.

Dans les deux cas, le taux de sur-échantillonnage est de 256 et la fréquence d'échantillonnage est de 8 MHz.

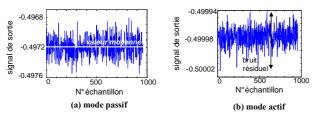

La figure 5 montre la sortie du convertisseur en fonction du temps en mode passif et actif. Le signal d'entrée est choisi constant égal à -0.5 (pour une pleine échelle normalisée entre -1 et 1).

La valeur moyenne du signal de sortie en mode passif est de -0.4972 alors qu'elle vaut -0.499998 en mode actif. Ainsi, l'erreur de non-linéarité – différence entre le signal

d'entrée et la valeur moyenne du signal de sortie — est équivalente à une résolution de 9.5 bits en mode passif et de 16.6 bits en mode actif. La précision peut se calculer à partir de la puissance de bruit résiduel. Elle est de l'ordre de 12.3 bits en mode passif et de 15.5 bits en mode actif. La linéarité est améliorée de 7 bits alors que la précision est améliorée de 3 bits.

Figure 5. Réponses transitoires pour une entrée statique de -0.5

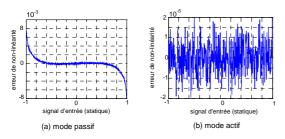

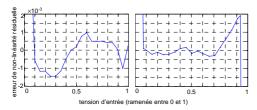

La figure 6 montre l'erreur de non-linéarité en fonction du signal d'entrée. La pleine échelle se situe entre -1 et +1. La figure 6(a) a été obtenue après une correction du premier ordre (ce qui suppose que le modulateur a été calibré pour déterminé son gain et son offset). Nous pouvons vérifier que le modulateur est fortement non linéaire pour des valeurs extrêmes. La figure 6(b) montre le bénéfice de la topologie active. Elle a été obtenue sans post-correction. Nous pouvons ainsi réaliser une conversion rail à rail avec une fonction de transfert DC fortement linéaire. L'erreur de non-linéarité reste inférieure à 2×10<sup>-5</sup> sur toute l'étendue d'entrée, ce qui équivaut à une résolution de 16.6 bits. Le bruit de quantification devient la source d'erreur prédominante.

Figure 6. Erreurs de non-linéarité en modes passif et actif.

#### 3.2 Largeur de bande

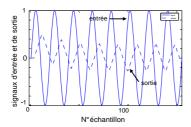

Nous avons ensuite effectué des simulations avec un signal d'entrée sinusoïdal de manière à comparer la largeur de bande des topologies actives simple et rapide. La figure 7 montre la réponse transitoire de la topologie simple pour un signal d'entrée de 20 KHz et une fréquence d'échantillonnage de 10 MHz : le gain est inférieur à 0.3 pour la topologie simple. Il est de 0.8 pour la topologie rapide.

Figure 7. Réponses transitoires avec une entrée sinusoïdale (fréquence d'entrée = 20kHz ; f<sub>e</sub> = 10MHz)

#### 4. Circuit réalisé

Un circuit prototype a été réalisé afin de valider le principe des topologies bi-modes et identifier les limitations.

L'étage numérique (A à F dans la figure 4) a été décrit en VHDL et implémenté sur une carte à base de circuits programmables ; les étages analogiques (G et H) ont été intégrés en technologie 0.35µm. Le circuit se compose :

- d'un comparateur ;

- d'un filtre à capacités commutées passif ;

- d'un filtre à capacités commutées actif;

- d'un générateur de masse virtuelle à VDD/2 ;

- d'un étage de commande des interrupteurs (à base de cellules numériques standard).

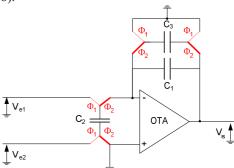

Le comparateur, le filtre passif et le générateur de masse virtuelle (VDD/2) ont été présentés dans l'article [5]. Pour le filtre actif, compte tenu de l'objectif visé par cette réalisation, nous avons privilégié la simplicité. Le circuit retenu est à sortie simple avec une seule capacité en entrée (figure 8).

Figure 8. Filtre actif à capacités commutées.

Sa fonction de transfert s'exprime ainsi :

$$\frac{V_S}{(V_{e_1} - V_{e_2})} = \frac{-\frac{C_2}{C_3} z^{-1}}{1 - \frac{C_1}{C_2} (1 - z^{-1})}$$

(5)

$V_{el}$  est le signal d'entrée à convertir est et  $V_{e2}$  est le signal de retour (délivré par le modulateur sigma-delta numérique). Comme  $V_{e2}$  est un signal binaire, cette entrée du filtre est connectée soit à la masse, soit à l'alimentation  $V_{DD}$  par un jeu d'interrupteurs adéquat. La référence des signaux (représentée par une masse virtuelle sur la figure 8) est  $V_{DD}/2$ . Elle est produite par un diviseur de tension à capacités commutées.

Cet amplificateur peut être contourné en mode passif. Dans ce cas, les sources de polarisation de l'amplificateur sont éteintes, de manière à réduire la consommation globale.

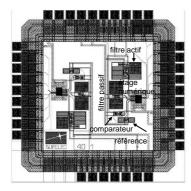

Le dessin du circuit intégré est représenté sur la figure 9. Tous les éléments ont été dupliqués pour des raisons liées au test

Figure 9. Dessin de masques de la puce

## 5. Résultats de mesures

#### 5.1 Linéarité

Les configurations testées sont les mêmes que celles décrites dans la partie 3. La tension d'alimentation est de 3.3 V. La précision de la mesure de la tension d'entrée est de l'ordre de 0.1%. En mode actif, les étages E et F ont été calibrés de manière à être appariés aux étages analogiques G et H

La figure 10 donne l'erreur de non-linéarité en fonction de la valeur de l'entrée (normalisée entre 0 et 1), en modes passif et actif (rapide). Les erreurs de gain et d'offset ont déjà été compensées. En mode passif, l'erreur de non-linéarité est inférieure à  $1.5\times10^{-3}$  dans la plage d'entrée [0.1 ; 0.9], ce qui correspond à une résolution équivalente de 9.3 bits. En mode actif, cette erreur est inférieure à  $4\times10^{-4}$  dans la plage [0.1 ; 0.7], ce qui correspond à une résolution équivalente à 11.3 bits. La non-linéarité augmente de façon drastique au-delà de 0.7.

Figure 10. Mesure de la non-linéarité

Ainsi, la linéarité est celle attendue en mode passif, mais les résultats en mode actif ne sont pas aussi bons que prévu. Des simulations complémentaires de haut niveau (non présentées ici), et au niveau transistor ont pu montrer que cette différence provient du filtre actif d'entrée. Le gain visà-vis de la tension de mode commun (e<sub>1</sub>+e<sub>2</sub>)/2 est trop élevé et surtout non linéaire. La forme de la réponse en mode commun de cet amplificateur se retrouve d'ailleurs dans la caractéristique DC du convertisseur.

## 5.2 Précision

La précision est calculée à partir du bruit résiduel à la sortie pour une entrée continue. Elle est de 9.6 bits en mode passif et de 12.3 bits en mode actif (rapide). La précision en mode passif est plus faible que celle obtenue par simulation à haut niveau. Les raisons sont les suivantes :

- effets d'injection de charge ;

sensibilité au bruit électronique dans la partie analogique (due à la faible amplitude de l'entrée du comparateur).

Nous retrouvons cependant 2.5 bits de différence entre les modes passif et actif (pour 3 bits attendus).

### 5.3 Largeur de bande

La largeur de bande mesurée sur la topologie active rapide est de l'ordre de 15 KHz, ce qui est compatible avec des applications audio.

#### 5.4 Consommation

La consommation mesurée pour une fréquence d'échantillonnage de 1MHz est de 1.4  $\mu A$  en mode passif et de 173  $\mu A$  en mode actif rapide. La consommation du filtre numérique n'a pas pu être mesurée.

#### 6. Conclusions

Cet article propose un système de conversion utilisant un modulateur sigma-delta passif et capable de fonctionner selon deux modes: un mode «faible consommation» (passif) et un mode « haute résolution » (actif). Les résultats expérimentaux valident le principe démontré au niveau fonctionnel et mettent en évidence les limitations. Une résolution expérimentale de 8 bits est atteinte en mode passif (modulateur passif suivi d'un filtre numérique) après une correction de gain et d'offset. La consommation de la partie analogique est inférieure à 2 uA pour une fréquence d'échantillonnage de 1 MHz. En mode actif, le modulateur est inséré dans une boucle contenant un filtre actif et des fonctions numériques. La résolution devrait théoriquement être augmentée de 6 bits. Les résultats expérimentaux montrent une résolution de 10.7 bits, mais elle devrait pouvoir être largement améliorée avec un filtre actif plus élaboré. Des études au niveau fonctionnel sont en cours pour analyser l'influence du choix du prédicteur, des défauts du filtre actif et d'un mauvais appariement des modèles numériques avec l'étage analogique.

#### 7. Remerciements

Ce travail est supporté par Texas Instruments Inc.

#### Références

- F.Chen, B.Leung, "A 0.25 mW low-pass passive sigma-delta modulator with built-in mixer for a 10 Mhz IF Input", IEEE Solid-State Circuits, SC-32, pp. 774-782, 1996.

- [2] T. Song, S. Yan, "A low power 1.1 MHz CMOS continuous-time delta-sigma modulator with active-passive loop filters", IEEE International Symposium on Circuits and Systems, May 2006.

- [3] P. Benabes., R. Kielbasa, «Passive sigma-delta converters design», IEEE Instrumentation and Measurement Technology, vol 1, pp. 469-474, Anchorage (Alaska), 21-23 May 2002.

- [4] P. Benabes, A. Gauthier, R. Kielbasa, "A Multistage Closed-Loop Sigma-Delta Modulator (MSCL)", *Journal of Analog Integrated Circuits and Signal Processing*, vol. 11, n° 3, pp. 195-204, Nov. 1996.

- [5] S.Guessab, P.Benabes, R.Kielbasa, "A passive delta-sigma modulator for low-power applications", IEEE International Midwest Symposium on Circuits and Systems, vol III, pp. 295-298, Hiroshima (Japan), July 25-28, 2004.