## Digital implementation of a BIST method based on binary observations

Christophe Le Blanc, Eric Colinet, Jérôme Juillard

#### ▶ To cite this version:

Christophe Le Blanc, Eric Colinet, Jérôme Juillard. Digital implementation of a BIST method based on binary observations. DSD, 11th Euromicro Conference on Digital System Design; Architectures, Methods and Tools, Sep 2008, Parme, Italy. pp. 709-713, 10.1109/DSD.2008.50. hal-00347177

### HAL Id: hal-00347177 https://centralesupelec.hal.science/hal-00347177

Submitted on 15 Dec 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Digital implementation of a BIST method based on binary observations

C. Le Blanc<sup>1</sup>, E.Colinet<sup>1</sup> and J. Juillard<sup>2</sup>

<sup>1</sup>CEA LETI, Minatec, Grenoble, France (<u>christophe.le-blanc@cea.fr</u>, <u>eric.colinet@cea.fr</u>)

<sup>2</sup>SUPELEC, SSE, Gif-sur-Yvette, France (<u>jerome.juillard@supelec.fr</u>)

Abstract—This article deals with a Built-in Self-Test method using only a one-bit ADC and a one-bit DAC, for use in a context of MEMS and microelectronics. It is theoretically possible to use a binary white noise and binary observations to estimate the impulse response and the output of a linear system, provided this system has good mixing properties. We show how this can be easily implemented on digital targets. The FPGA-based identification of the impulse response of a bandpass filter is performed and the experimental results are presented.

#### I. INTRODUCTION

One of the major issues when designing micro electromechanical systems (MEMS) is possible dispersions due to variations in the manufacturing process, environmental variations (pressure, temperature), ageing. The MEMS behavior can differ drastically from what is expected. In order to achieve optimal performances, there is a need for devices with self-test and self-adjustment capacities [1][2]. This article focuses on a real time algorithm that can be used to identify the impulse response of a MEMS device. As opposed to existing identification methods [3], the proposed approach does not require high resolution analog to digital converters. These issues are addressed in [4] where the Basic Identification Method using Binary Observations (BIMBO) is presented. In its simplest version, BIMBO is an iterative offline algorithm, whose performances depend on the quality of the guess of the initial model parameters. An initialization method for the BIMBO algorithm that addresses this issue is presented in [5]. This initialization method, which relies on the estimation of the covariance of the system's binary inputs and outputs, can be deployed in real time and used as a standalone identification method. This paper describes improvements of the approach presented in [5] that are suitable for its hardware implementation on a digital target (FPGA, DSP). In the first part of the paper, the principle of the algorithm is presented. Then, its digital implementation is described. The corresponding architecture is based on multiplexing: as a consequence, the number of equivalent ASIC gates is minimized, but the execution speed is reduced. In the last part, some practical examples are given to illustrate the efficiency of the approach.

#### II. BACKGROUND

#### A. Framework

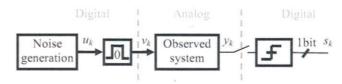

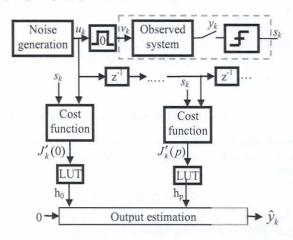

Let us make the assumption that the MEMS under test can be modeled as an LTI system and that it can be described by the first  $n_k$  coefficients of its impulse response  $(h_0, \ldots, h_{n_k-1})$ . The method presented in [1] can be used to identify these coefficients based on the knowledge of the system input  $u_k$  and of the sign  $s_k$  of the system output  $y_k$  (Fig. 1). The input signal may either be a binary or Gaussian white noise. This paper deals with binary white noise for two reasons. First, a binary white noise is easier to generate than a Gaussian one since the implementation of a binary white noise generator only requires one linear feedback shift register (LFSR). The other reason is that the conversion from digital to analog of a binary signal is less costly (in terms of silicon area) than that of a Gaussian signal.

Figure 1. Experimental setup and notations,  $u_k \in \{0,1\}$ ,  $v_k \in \{-1,1\}$ ,  $s_k \in \{0,1\}$

Notice that, due to the 1-bit ADC, there is a loss of amplitude information: multiplying the gain of the unknown system by any positive constant does not affect  $s_k$ . In order to identify the gain of the system, one would have to add an amplitude reference (such as an offset or a dithering signal) at the input of the comparator. However, in the scope of this article, we concentrate on the simpler situation represented in Fig. 1: as a consequence, only the relative amplitude of the coefficients of the impulse response will be identified.

#### B. Principle of the proposed approach Under the following 2 conditions:

- $u_k$  is a binary white noise,

- the impulse response of the tested system does not vanish quickly or, in other words, the tested system has good mixing properties.

an estimation of the p<sup>th</sup> coefficient of the impulse response is given by [5]:

$$\hat{h}_p = G \frac{\text{erf}^{-1}(-2J_k(p))}{\sqrt{1 + 2(\text{erf}^{-1}(-2J_k(p)))^2}},$$

(1)

where  $\operatorname{erf}^{-1}$  is the inverse error function and  $J_k(p)$  is given by:

$$J_k(p) = \frac{1}{k+1} \sum_{l=0}^{k} (u_{l-p} - s_l)^2, \qquad (2)$$

and G is a positive coefficient that can be chosen once and for all. For the sake of simplicity, we choose G = 1. Note that  $J_k(p)$  may also be written:

$$J_k(p) = \frac{1}{2} (1 - C_{su}(p)),$$

(3)

where  $C_{su}(p)$  is an empirical estimate of the cross-covariance of  $s_k$  and  $u_k$  [5]. It is then possible to construct an "estimate"  $\hat{y}_k$  (bearing in mind that some amplitude information was lost) of the system output using:

$$\hat{y}_k = \sum_{p=0}^{n_k} \hat{h}_p v_{k-p} \ . \tag{4}$$

At each sample time, the identification process is then divided in five steps:

- A. generation of a noise sample  $u_k$ ,

- B. acquisition of the observed binary output signal,

- C. estimation of  $J_k(p)$ ,  $0 \le p < n_h$

- D. estimation of the impulse response,

- E. reconstruction of the system output.

In section III, we describe a practical implementation of this approach.

#### III. ARCHITECTURE

In the next five sub-sections, we present a hardware architecture that implements the above-mentioned steps with a very moderate cost.

#### A. Noise generation

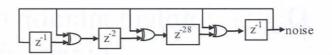

In order to generate 1-bit white noise signal, a Galois Linear Feedback Shift Register (LFSR) of order 32 has been implemented (Fig. 2) [6]

Figure 2. Noise generator structure

#### B. Acquisition of binary outputs

In order to identify the coefficients of the impulse response, the last  $n_h$  values of  $u_k$  must be stored: this is accomplished by using a  $n_h$ -long delay line. As for the binary output of the system, only its current value  $s_k$  must be stored, as long as  $J_k$  is estimated iteratively, as described in subsection C.

#### C. Estimation of $J_{\nu}$

Since  $u_k$  and  $s_k$  take only binary values 0 and 1,  $J_k$  may be written:

$$J_k(p) = \frac{1}{k+1} \sum_{l=0}^{k} XOR(s_l, u_{l-p}),$$

(5)

or as a recurrence relation:

$$J_{k}(p) = \frac{XOR(s_{k}, u_{k-p}) + kJ_{k-1}(p)}{k+1}.$$

(6)

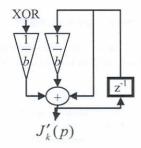

A possible physical implementation of (6) is shown in Fig.3. However, this solution requires a division by an integer. Moreover, this integer goes to infinity as the number of observations increases: as a consequence, the solution presented in Fig. 3 is unpractical.

Figure 3. Exact calculation of  $J_k$

Looking at  $J_k(p)$  as the average value of  $XOR(s_l, u_{l-p})$  over the last k samples, it is simple to see that expression (7) and the corresponding recurrence relation (8) will give a good approximation of  $J_k(p)$  when integer b and the number of samples are large:

$$J'_{k}(p) = \frac{1}{b} \sum_{l=0}^{k} \left(1 - \frac{1}{b}\right)^{k-l} XOR(u_{l-p}, s_{l})$$

(7)

$$J'_{k}(p) = \frac{XOR(u_{k-p}, s_{k}) + (b-1)J'_{k-1}(p)}{b},$$

(8)

In (7-8), b acts as a forgetting factor: as the value of b decreases, the weight of new observations increases and  $J_k'(p)$  gives a poorer approximation of  $J_k(p)$ . b can be chosen to be a power of two so that the division in (8) becomes a simple shift operation. The physical implementation of equation (8) is shown in Fig. 4. Notice that no complex logic is now needed to estimate  $J_k(p)$ .

Figure 4. Approximate calculation of  $J_k$

#### D. Estimation of the impulse response

In order to compute the coefficients of the impulse response from  $J'_k$ , equation (1) must be used. Since  $J'_k$  is bounded, a look-up table (LUT) can be used to evaluate the right-hand side of (1). The LUT coefficients are stored in a ROM which is addressed by the cost function.

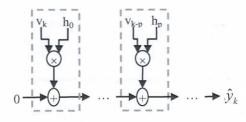

#### E. Reconstruction of the system output

The "estimate"  $\hat{y}_k$  of the system output can then be computed by convolution of the estimated impulse response with the system inputs. This can be done with the hardware implementation depicted in Fig. 5. The multiplication blocks appearing in Fig. 4 are in fact logic OR gates since  $u_k$  is a binary signal.

Figure 5. Calculation of  $\hat{y}_k$

#### F. Global architecture

The real-time hardware architecture is shown in Fig. 6. Notice that the output signal  $\hat{y}_k$  and impulse response coefficients are at each sample time updated by new observations. This architecture has been described in VHDL and implemented into a Xilinx Virtex 2v6000 FPGA. The whole system occupies less than 160k equivalent ASIC gates to estimate 100 impulse response coefficients. The maximum sampling frequency is about 10 MHz.

Figure 6. Global architecture

#### IV. TESTS - EXAMPLE

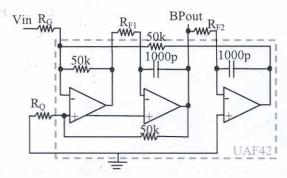

The algorithm has been tested on a universal active filter (UAF) [7] represented in Fig. 7. The sampling frequency is 15 kHz. The nominal values of the quality factor  $\mathcal Q$  and of the natural frequency  $f_0$  can be calculated analytically. For the values of the resistances given in Fig. 7, we find  $\mathcal Q$ =1.2 and  $f_0$ =730 Hz. However, one might expect some discrepancies between these values and the actual ones, because of physical dispersions.

Figure 7. Bandpass configuration of a UAF. RF1=RF2=220k $\Omega$ ; RG=22k $\Omega$ ; RQ=10k $\Omega$

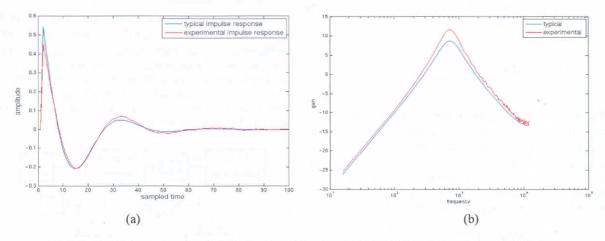

These discrepancies are confirmed by a test of the circuit, using the hardware architecture described in section III. The first 100 coefficients of the impulse response are identified and the results obtained after 40000 samples of the output have been processed are shown in Fig. 8 and compared to the

Figure 8. Comparison between nominal (blue) and experimental results (red): (a) impulse response, (b) transfer function

nominal impulse response and transfer function. One can see that the identified system is slightly more resonant than expected.

#### V. CONCLUSION

We have presented a hardware implementation of the online BIST method introduced in [5], for estimating the impulse response of an unknown linear system. The only analog components required in this approach are a one-bit DAC and a one-bit ADC. We have shown how the fact that the inputs and outputs of the system are binary can be put to good use in the hardware implementation of the approach and the corresponding architecture can easily be implemented on an FPGA target, as shown in section III. A universal active filter was used to illustrate the performances of the proposed approach. Convergence acceleration procedures for the

presented method and identification of infinite impulse response models are the subject of ongoing work.

#### REFERENCES

- Landau I. D., Zito G., "Digital control design. Design, identification, implementation", Springer, 2006, ISBN 1-84628-055-9

- [2] Soderstrom T., Stoica P., "System identification", Prentice Hall 1988, ISBN 0138812365

- [3] E.Colinet, "Nouvelles architectures et méthodes de conception de microsystèmes sigma-delta et de microsystèmes résonants"

- [4] E. Colinet, J. Juillard, "Identification of a one-bit lowpass sigma delta modulator using BIMBO", IMTC 2007

- [5] J. Juillard, E. Colinet, "Initialization of the BIMBO self-test method using binary inputs and outputs", CDC 2007

- [6] D. W. Clark and Lih-Jyh Weng, "Maximal and Near-Maximal Shift Register, Sequences: Efficient Event Counters", IEEE TRANSACTIONS ON COMPUTERS, VOL. 43, NO. 5, MAY 1994

- [7] Texas Instrument, "Universal Active Filter", UAF42 Datasheet