## A new two-step $\Sigma\Delta$ architecture column-parallel ADC for CMOS image sensor

Pierre Bisiaux, Caroline Lelandais-Perrault, Anthony Kolar, Philippe Benabes, Filipe Vinci dos Santos

#### ▶ To cite this version:

Pierre Bisiaux, Caroline Lelandais-Perrault, Anthony Kolar, Philippe Benabes, Filipe Vinci dos Santos. A new two-step  $\Sigma\Delta$  architecture column-parallel ADC for CMOS image sensor. 29th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), Aug 2016, Belo Horizonte, Brazil. 10.1109/SBCCI.2016.7724065 . hal-01357892

### HAL Id: hal-01357892

https://centrale supelec.hal.science/hal-01357892v1

Submitted on 1 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A new two-step $\Sigma\Delta$ architecture column-parallel ADC for CMOS image sensor

Pierre Bisiaux, Caroline Lelandais-Perrault,

Anthony Kolar and Philippe Benabes

GeePs | Group of electrical engineering - Paris, UMR CNRS 8507,

CentraleSupelec, Univ Paris-Sud, Universite Paris-Saclay

Sorbonne Universites, UPMC Univ Paris 06

3 &11 rue Joliot Curie, Plateau de Moulon

F91192 Gif sur Yvette CEDEX France

Email: Pierre.Bisiaux, Caroline.Lelandais-Perrault, Anthony.Kolar, Philippe.Benabes@centralesupelec.fr

Filipe Vinci Dos Santos Chair on Advanced Analog Design 3, rue Joliot CuriePlateau de Moulon 91192 Gif-Sur-Yvette Cedex

Email: Filipe.Vinci@centralesupelec.fr

Abstract—The demand for high resolution CMOS image sensors (CIS) is rising. Analog-to-digital converters (ADC) represent one of the major bottleneck of CIS. One of the candidates to overcome the existing limits is the column-parallel ADC. Column-parallel extended counting ADCs (EC-ADC) are able to reach high resolution thanks to their two-step conversion. However the EC-ADC area increases due to the two-step design. A solution is to use the same hardware twice to perform both steps. This paper proposes a 14-b, 100 kHz Nyquist frequency, two-step incremental  $\Sigma\Delta$  (I $\Sigma\Delta$ ) analogto-digital converter suitable for column-parallel CIS. Several architectures with different modulator order are compared to determine the most promising one. The proposed architecture, compared to a one-step second order modulator, reduces the total oversampling ratio (OSR) from 150 to 60 to reach a resolution of 14-b. The operational transconductance amplifiers (OTA) is the most critical part in our ADCs. Its required DCgain is around 80 dB for a 120 MHz gain-bandwidth product (GBW). The ideal DNL and INL of our two-step I $\Sigma\Delta$  ADC are respectively +0.55/-0.6 LSB and +0.5/-0.5 LSB. This work achieves a SNDR of 89 dB when a full scale sinusoid of 100 kHz is applied.

Index Terms—ADC, incremental, sigma-delta  $(\Sigma\Delta),$  two-step, CMOS Image Sensor, column-parallel ADC, second-order  $\Sigma\Delta$

#### I. Introduction

High quality CMOS image sensors (CIS) have become indispensable in the aerospace field. This evolution is possible thanks to the progress in the integration of sensor, readout electronics and A/D conversion in a single chip. The increasing resolution of the image sensor restricts the pitch of the pixel. This also increases the rate of pixel data conversion for a given frame rate. Moreover, greater pixel sensitivity and dynamic range demand 12-bits or higher resolution conversion. The column-parallel conversion is seen as the best answer to these increasingly stringent requirements.

Among column-parallel ADCs, single-slope (SS-ADC) and successive approximation register (SAR) ADCs are usually chosen for low power consumption application [1] [2] [3] [4]. However, the SS-ADC requires a large amount

of clock cycles for high resolution conversion. The SAR ADC needs a capacitor DAC consuming large area due to the weight of the capacitor and is very sensitive to the capacitor mismatch. Cyclic ADCs are also widely used in the CIS field [5] [6] [7]. This ADC only requires n clock cycles for a n-bit resolution. However, cyclic ADCs require high DC gain OTA to avoid non-linearity. Matching problems limit the resolution achievable by cyclic ADCs. Sigma-Delta  $(\Sigma\Delta)$  ADCs are well known for their ability to achieve high resolution. However they are slower than Nyquist converters due to oversampling.  $\Sigma\Delta$  ADCs have recently appeared in CIS field thanks to the scaling down technology [8] [9].  $\Sigma\Delta$  ADCs require smaller DC gain and sampling capacitance than cyclic ADCs because of the oversampling operation.

In order to achieve a better tradeoff between speed and resolution, extended-counting ADCs (EC-ADC) have been reported [10] [11]. The EC-ADC is an hybrid architecture that performs the conversion in two steps. First a coarse conversion is done using an incremental  $\Sigma\Delta$  (I $\Sigma\Delta$ ) ADC. The first step generates an analog residue. Then the fine conversion of the residue is realized with a Nyquist converter. Thus the overall conversion time is reduced compared to a single step I $\Sigma\Delta$ . However EC-ADCs have quite complex circuits due to the use of two different conversion principles. The two-step conversion can be pushed further and both conversions can be realized by the same  $I\Sigma\Delta$  ADC. Such architectures are known as two-step I $\Sigma\Delta$  ADCs [12] [13]. The two-step  $I\Sigma\Delta$  ADCs advantage is to use twice the same hardware for both conversions, while simultaneously decreasing the overall OSR. In order to obtain a higher resolution (compared to a single loop  $I\Sigma\Delta$ ) and limit the complexity of the circuit, a two-step  $I\Sigma\Delta$  ADCs can be preferable over EC-ADCs. In this paper, a two-step second order I $\Sigma\Delta$  ADC is proposed. The remainder of this paper is organized as follows : section II describes the  $I\Sigma\Delta$ modulator. In section III a two-step  $I\Sigma\Delta$  architecture and its characteristics are described. In section IV the high level modulator design is discussed. Then the section V presents

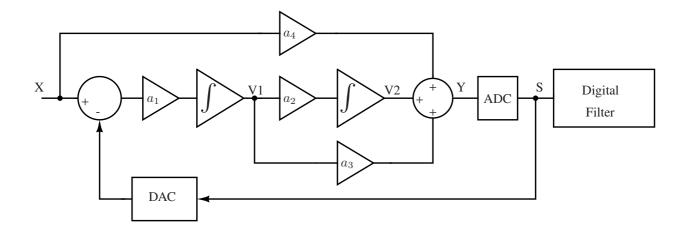

Figure 1.  $2^{nd}$  order modulator with feed-forward path

the simulated ADC characteristics.

#### II. INCREMENTAL $\Sigma\Delta$ ADC

The first  $I\Sigma\Delta$  ADC was published by Van De Plassche in 1978 [14]. It is composed of an integrator, an ADC (a comparator with 2 levels in most cases) and a digital-toanalog converter (DAC) in the feedback path. This architecture has the drawback to be very slow. Indeed it requires  $2^n$  clock cycles to reach *n*-bits. To improve the conversion speed, one can increase the modulator order or the number of cascaded modulators. However, higher order modulators can lead to stability problems which are hard to solve. An example of a  $I\Sigma\Delta$  with a second order modulator is shown in fig.1. Here, the  $I\Sigma\Delta$  is studied in the time domain. In this way the residue value can be written depending on  $\Sigma\Delta$ modulator parameters and the result is reused later for the two-step architecture. In this architecture the output of the integrators are given by

$$V_1[M] = a_1 \sum_{i=1}^{M-1} (X[i] - S[i])$$

(1)

$$V_1[M] = a_1 \sum_{i=1}^{M-1} (X[i] - S[i])$$

$$V_2[M] = a_1 a_2 \sum_{K-1}^{M-1} \sum_{i=1}^{K-1} (X[i] - S[i])$$

(2)

where M is the OSR. After M clock cycles the error of conversion is given by

$$E = X - \hat{X} = \frac{2}{a_1 a_2 M(M-1)} . V_2[M]$$

(3)

where  $\hat{X}$  is the estimated reconstructed signal from the bitstream, defined as,

$$\hat{X} = \frac{2}{M(M-1)} \sum_{K=1}^{M-1} \sum_{i=1}^{K-1} S[i]$$

(4)

One can observe that the residue value  $V_2(M)$  is the image of the conversion error. With this modulator, 150 cycles are needed to reach 14 bits resolution [15].

#### III. TWO-STEPS I $\Sigma\Delta$ ADC

#### A. Two-steps architecture

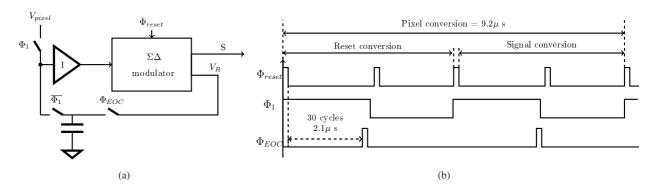

For several years, architectures with reused hardware have been investigated to decrease the size of the ADC [16] [17]. In a two-step IS $\Delta$  ADC [12] [18], the conversion is divided in 2 phases and the hardware is used twice to perform the full conversion. The chosen architecture and its diagram timing are shown in fig.2.

The architecture is composed of a sample-and-hold (S/H), an I $\Sigma\Delta$  modulator and a digital filter. At the beginning of the conversion, a reset is done on the integrators and the capacitors. During the first step ( $\Phi$ 1=1) the pixel value is fed to the modulator. At the end of the coarse conversion  $(\Phi_{EOC} = 1 \text{ and } \Phi 1=0)$ , the residue  $V_R$  (or  $V_2[M]$ ) is loaded into the S/H. Then another reset is done and the fine conversion is performed. The timing diagram for a conversion is shown in fig. 2(b). To reach 100 frames/s (FPS) with a 1920x1080 array, the available row time is 9.2  $\mu$ s. Two conversions are realized within the row time to do a correlated double sampling in digital domain. Since a few extra clock cycle are necessary to reorganize the switch and load the capacitance, a single step can last up to 2.1  $\mu$ s.

#### B. Modulator scaling

As already mentioned the residue of the coarse conversion is used for the fine conversion. The goal is to fit the output of the first step to the input of the second step. Moreover the input range of a  $2^{nd}$  order modulator must be limited to avoid integrator overflow. So it is very important to limit the residue value. The chosen modulator is shown in fig.1. As one can see in eq.(3), a solution to modify  $V_R$  is to modify the parameter  $a_{1,2}$  of the modulator. In fig.1, parameters  $a_1$ and  $a_2$  are arbitrary chosen at 0.5 and the maximum input at 75% of the reference. An optimization is performed by sweeping parameters  $a_3$  and  $a_4$  to minimize the swing of the signals into the integrators giving  $a_3 = 2$  and  $a_4 = 1$ . Then a global scaling coefficient is applied to fit the output swing

Figure 2. High-level view of (a) two-steps architecture with  $2^{nd}$  order modulator and (b) the timing diagram of the conversion

of the integrator with the input range of the modulator. The optimum coefficients are  $a_1 = 0.75$ ,  $a_2 = 0.5$ ,  $a_4 = 1.5$  and  $a_3 = 2$ . However these optimal values are not very convenient to implement in switched capacitor circuit. Moreover a margin has to be taken from optimal coefficients to be insensitive to analog mismatches. At the end, the final values are  $a_1 = a_2 = 0.5$ ,  $b_1 = 1$  and  $a_3 = 2$ .

From eq.(3) a total of 27 cycles per step is needed to reach 7-b of resolution. In order to get some margin to deal with analog mismatches, the OSR is increased to 30 leading to a total OSR of 60 for a conversion giving 70 ns per cycle. Once again, a small margin is taken giving a clock frequency of 20 MHz.

#### C. OSR split of two-steps conversion

We previously supposed that the length of both steps were equal. This supposition is verified in the following part as the optimal choice. The parameters  $k1=a_1.a_2.M_1(M_1-1)/2$  and  $k2=a_1.a_2.M_2(M_2-1)/2$  are introduced with  $M_1$  and  $M_2$  respectively the OSR of the first and the second step. From eq.(3), one can derive the error of the conversion,

$$E_{TOT} = \frac{V_{FS}}{k1.k2} = \frac{4}{a_1^2.a_2^2.M_1(M_1 - 1).M_2(M_2 - 1)}.V_{FS}$$

$$E_{TOT} \approx \frac{4}{a_1^2.a_2^2.M_1^2.M_2^2}.V_{FS}$$

(5)

Setting  $M=M_1+M_2$  and  $\alpha=M_1/M_2$ , eq.(5) can be written,

$$E \approx \frac{4.V_{FS}}{\frac{a_1^2 a_2^2 \alpha^2.M^4}{(\alpha+1)^4}} \tag{6}$$

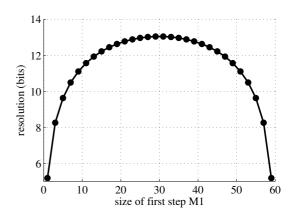

From eq.(6), one can plot the curve shown in fig. 3. As one can see the resolution is maximum when the OSR is equal in both steps.

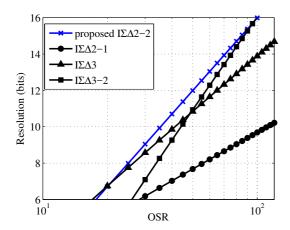

The choice of the modulator order for the two steps is now discussed. In recent two-step  $I\Sigma\Delta$  ADC work, the modulator order can be different for the two-step [18]. For second and higher order modulator, the last integrator can be switched to a sample-and-hold for the second step. The modulator order of the second step is then decreased of one order. The analysis of the modulator order within the conversion is now studied. Four different architectures are compared: a third order modulator single loop ( $I\Sigma\Delta 3$ ), a

Figure 3. resolution of the conversion for different size of the first conversion

two-step with a second and first order modulator ( $I\Sigma\Delta 2$ -1), a two-step with two second order modulator ( $I\Sigma\Delta 2$ -2) and a two-step with a third order and second order modulator ( $I\Sigma\Delta 3$ -2). The result of our simulations is shown in fig.4. The resolution of the different ADC is calculated from the conversion error, computed using eq.(5). In each case, integrators modulators coefficients and  $\alpha$  in eq.(6) are optimized to minimize the conversion error, thus maximize the resolution. In the different architectures, input range is reduced to avoid integrator overflow. Considering the scaling of the different architectures and the aimed resolution, the proposed  $I\Sigma\Delta 2$ -2 architecture requires the smallest OSR.

#### IV. MODULATOR SPECIFICATIONS

In this section, the switched capacitor circuit and the modulator characteristics are presented. The effect of non-idealities in the OTA (finite DC gain, gain bandwidth-product (GBW) and slew rate (SR)) are introduced and their effects simulated. In this part and for the rest of the paper, the resolution is calculated from the SNDR.

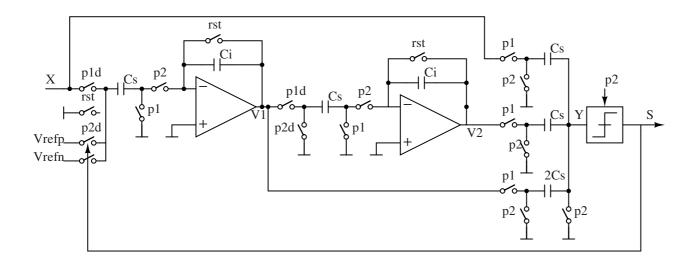

#### A. Switched-capacitor circuit

The switched-capacitor circuit implementation is shown in fig. 5. A single-ended version of the architecture is represented to simplify the circuit. The sampling capacitance

Figure 4. comparison of different architectures and modulator order

$C_s$  is chosen to be 100 fF. The integrators realized with the OTA are the most critical part in a modulator. To minimize injection charge effect, two non overlapped clock p1 and p2, and their delayed signal p1d and p2d, are used

The characteristics of the OTA are now discussed. The DC gain OTA, the GBW and the slew-rate (SR) are important parameters in a switched capacitor circuit. These parameters are degrading the charge transfer and introduced errors at both input and output of the integrator.

#### B. Finite OTA DC gain

The finite DC gain OTA introduces an offset at the input of the integrators. The transfer function of the integrator with an finite OTA DC gain is expressed as follow

$$Vo(n) = \frac{(1+\mu)Vo(n-1) + \frac{C_s}{C_i}Vin(n-1)}{1 + \mu(1 + \frac{C_s}{C_i})}$$

(7)

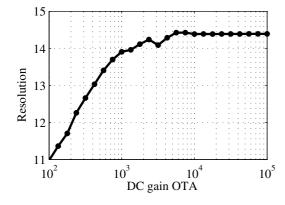

with Vo the output of the integrator, Vin the input,  $\mu=1/Ao$ , with Ao the finite DC gain,  $C_s$  and  $C_i$  respectively the sampling and the integrator capacitance. The simulation is shown in fig.6. One can see that the resolution drops from a DC gain of 5000, or 74 dB. Thus a minimum DC gain of 80 dB is chosen.

Figure 6. DC gain OTA versus ENOB

#### C. Finite GBW and SR

The charge transferring phase of a switched-capacitor circuit can be cut into a slewing and a settling part. Finite SR and GBW respectively influence the slewing and the settling time. The influence of the GBW on the system is first analysed. The transfer function of an integrator with a finite GBW is

$$Vo(n) = Vo(n-1) + \frac{C_s}{C_i} \left( 1 - \exp^{-k_1} \left( \frac{C_s}{C_s + C_i} \right) \right)$$

(8)

with

$$k1 = \left(\frac{GBW.C_i}{C_i + C_s}\right) \left(\frac{T}{2}\right) \tag{9}$$

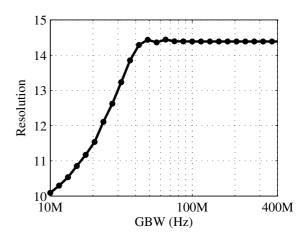

with Vo and the Vin respectively the output and the input of the integrator and T the available settling time. The result of the simulation is shown in fig 7. One can see that the

Figure 7. DC gain OTA versus ENOB

resolution quickly dropped for a GBW below 50 MHz. However this value is quite small considering the settling time. Thus a GBW of 120 MHz is chosen to be at least five times higher than the clock frequency. The slewing time is then determined to calculate the SR. A good trade-off is to set the slewing time at 25% of the available time. The remaining time is used for the settling time. The SR is expressed by

$$SR = \frac{\Delta V}{T_{slewing}} \tag{10}$$

with  $\Delta V$  the maximum output swing of the integrator and  $T_{slewing}$  the chosen slewing time. The minimum SR calculated is 220 V/ $\mu$ s. The values found previously are put together in table I.

#### V. RESULTS

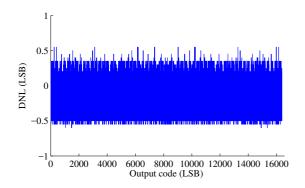

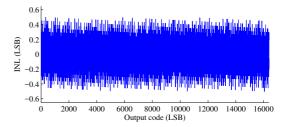

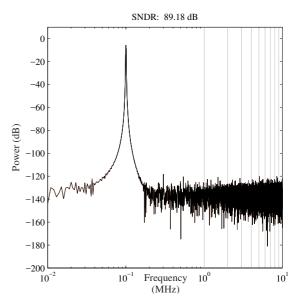

An ideal model of the proposed ADC is used to compute the DNL and the INL of the ADC. The ideal DNL and the INL of the I $\Sigma\Delta$  are shown in fig.8 and fig.9. The DNL and INL of the ADC are respectively +0.55/-0.6 LSB and +0.5/-0.5 LSB. The ADC output spectrum is shown in fig.10. The SNDR is calculated with a full scale input signal of 100 kHz

Figure 5.  $2^{nd}$  order modulator with feed-forward path

Table I OTA CHARACTERISTICS

| Slew rate        | 220 V/μs |

|------------------|----------|

| GBW              | 120 MHz  |

| Load capacitance | 300 fF   |

| DC gain          | 80 dB    |

and a sampling frequency of 20 MHz. This ADC achieves a SNDR of 89 dB. The power consumption is estimated from schematic simulation and is  $450\mu W$ . The performance comparison with others EC-ADC is shown in table II.

Figure 8. DNL of proposed ADC

#### VI. CONCLUSION

This paper presents a two-step  $I\Sigma\Delta$  for column-parallel conversion of pixel arrays, allowing a monolithic integration of the whole CIS. First, several architectures are compared to analyze the one reaching the highest resolution with the lowest OSR. Compared to a single loop second order modulator, the proposed two-step ADC with second order

Figure 9. INL of proposed ADC

Figure 10. ADC output spectrum

modulator ( $I\Sigma\Delta 2$ -2) can reduce the OSR from 150 to 60, to reach 14-b of resolution. Simulations are then realized to get OTA specifications that avoid lowering the resolution of the ADC. To finish simulations on ideal ( $I\Sigma\Delta 2$ -2) ADC

Table II PERFORMANCE COMPARISION

|                      | [11]                   | [19]                | [10]                   | [12]                 | This work            |

|----------------------|------------------------|---------------------|------------------------|----------------------|----------------------|

| Technology (µm)      | 0.18                   | 0.35                | 0.18                   | 0.15                 | 0.18                 |

| ADC architecture     | $\Sigma\Delta$ +Cyclic | $\Sigma\Delta$ +SAR | $\Sigma\Delta$ +Cyclic | 2step $\Sigma\Delta$ | 2step $\Sigma\Delta$ |

| Sampling rate (kS/s) | 30                     | 150                 | 50                     | -                    | 100                  |

| Resolution           | 17                     | 14.3                | 10.2                   | 12                   | 14                   |

| Power (µW)           | 345                    | 300                 | 13                     | 363                  | 410                  |

| DNL (LSB)            | -0.88/1.38             | -0.79/0.97          | -                      | -0.7/1.8             | -0.55/0.6            |

| INL (LSB)            | -26.3/35               | -1.7/2.79           | -                      | -22/20               | -0.5/0.5             |

| SNDR (dB)            | 85                     | -                   | 63                     | -                    | 89                   |

are performed giving DNL/INL characteristics and the ADC output spectrum.

#### REFERENCES

- [1] MF Snoeij, AJP Theuwissen, and JH Huijsing. A low-power columnparallel 12-bit adc for cmos imagers. In Proc. IEEE Workshop Charge Coupled Devices (CCDs) and Advanced Image Sensors (AIS), pages 169–172, 2005.

- [2] Min-Seok Shin, Jong-Boo Kim, Min-Kyu Kim, Yun-Rae Jo, and Oh-Kyong Kwon. A 1.92-megapixel cmos image sensor with columnparallel low-power and area-efficient sa-adcs. *Transactions on Electron Devices*, 59(6):1693–1700, June 2012.

- [3] Li Quanliang. A 12-bit compact column-parallel sar adc with dynamic power control technique for high-speed cmos image sensors. *Journal* of Semiconductors, 35(10):1–8, october 2014.

- [4] D.G. Chen, Fang Tang, Man-Kay Law, Xiaopeng Zhong, and A. Bermak. A 64 fj/step 9-bit sar adc array with forward error correction and mixed-signal cds for cmos image sensors. *Circuits and Systems I: Regular Papers, IEEE Transactions on*, 61(11):3085–3093, Nov 2014.

- [5] Mitsuhito Mase. A wide dynamic range cmos image sensor with multiple exposure-time signal outputs and 12-bit column-parallel cyclic a/d converters. JSSC, 40(12):2787–2795, December 2005.

- [6] Jong-Ho Park, S. Aoyama, T. Watanabe, K. Isobe, and S. Kawahito. A high-speed low-noise cmos image sensor with 13-b column-parallel single-ended cyclic adcs. *Electron Devices, IEEE Transactions on*, 56(11):2414–2422, Nov 2009.

- [7] Seunghyun Lim, Jimin Cheon, Youngcheol Chae, Wunki Jung, Dong-Hun Lee, Minho Kwon, Kwisung Yoo, Seogheon Ham, and Gunhee Han. A 240-frames/s 2.1-mpixel cmos image sensor with columnshared cyclic adcs. *Solid-State Circuits*, *IEEE Journal of*, 46(9):2073– 2083. Sept 2011.

- [8] A. Mahmoodi and D. Joseph. Optimization of delta-sigma adc for column-level data conversion in cmos image sensors. In *Instrumentation and Measurement Technology Conference Proceedings*, 2007. IMTC 2007. IEEE, pages 1–6, May 2007.

- [9] Youngcheol Chae, Jimin Cheon, Seunghyun Lim, Minho Kwon, Kwisung Yoo, Wunki Jung, Dong-Hun Lee, Seogheon Ham, and Gunhee Han. A 2.1 m pixels, 120 frame/s cmos image sensor with column-parallel  $\delta\sigma$  adc architecture. *Solid-State Circuits, IEEE Journal of*, 46(1):236–247, Jan 2011.

- [10] Cencen Gao, Dong Wu, Hui Liu, Nan Xie, and Liyang Pan. An ultralow-power extended counting adc for large scale sensor arrays. In Circuits and Systems (ISCAS), 2014 IEEE International Symposium on. pages 81–84. June 2014.

- [11] Min-Woong Seo. A low-noise high-dynamic-range 17b 1.3megapixel 30-fps cmos image sensor with column-parallel two-stage folding-integration/cyclic adc. *Transactions on Electron Devices*, 59(12):3396–3400, november 2012.

- [12] Y. Oike and A. El Gamal. Cmos image sensor with per-column  $\sigma\delta$  adc and programmable compressed. *Solid-State Circuits, IEEE Journal of*, 48(1):318–328, Jan 2013.

- [13] Mengyun Yue, Dong Wu, and Zheyao Wang. A 15-bit two-step sigmadelta adc with embedded compression for image sensor array. In Circuits and Systems (ISCAS), 2013 IEEE International Symposium on, pages 2038–2041, May 2013.

- [14] R.J. van de Plassche. A sigma-delta modulator as an a/d converter. Circuits and Systems, IEEE Transactions on, 25(7):510–514, Jul 1978.

- [15] Biao Wang. A 1.8-v 14-bit inverter-based incremental sd adc for cmos image sensor. In ASICON, editor, ASICON. ASICON, IEEE, 2013.

- [16] Min-Woong Seo, Sung-Ho Suh, T. Iida, T. Takasawa, K. Isobe, T. Watanabe, S. Itoh, K. Yasutomi, and Shoji Kawahito. A lownoise high intrascene dynamic range cmos image sensor with a 13 to 19b variable-resolution column-parallel folding-integration/cyclic adc. Solid-State Circuits, IEEE Journal of, 47(1):272–283, Jan 2012.

- [17] Jae hong Kim, Wun ki Jung, Seung hyun Lim, Yu jin Park, Won ho Choi, Yun jung Kim, Chang eun Kang, Ji hun Shin, Kyo jin Choo, Won baek Lee, Jin kyeong Heo, Byung jo Kim, Se jun Kim, Min ho Kwon, Kwi sung Yoo, Jin ho Seo, Seog heon Ham, Chi young Choi, and Gab soo Han. A 14b extended counting add implemented in a 24mpixel aps-c cmos image sensor. In Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2012 IEEE International, pages 390–392, Feb 2012.

- [18] C.-H. Chen, Y. Zhang, T. He, P.Y. Chiang, and G.C. Temes. A micropower two-step incremental analog-to-digital converter. *Solid-State Circuits*, *IEEE Journal of*, PP(99):1–13, 2015.

- [19] M.-S. Shin, J.-B. Kim, and O.-K. Kwon. 14.3-bit extended counting adc with built-in binning function for medical x-ray cmos imagers. *Electronics Letters*, 48(7):361–363, March 2012.