# Integration of ammonia-plasma-functionalized graphene nanodiscs as charge trapping centers for nonvolatile memory applications

Jer-Chyi Wang, Kai-Ping Chang, Chih-Ting Li, Ching-Yuan Su, Fethullah Güneş, Mohamed Boutchich, Chang-Hsiao Chen, Ching-Hsiang Chen, Ching-Shiun Chen, Lain-Jong Lai, et al.

# ▶ To cite this version:

Jer-Chyi Wang, Kai-Ping Chang, Chih-Ting Li, Ching-Yuan Su, Fethullah Güneş, et al.. Integration of ammonia-plasma-functionalized graphene nanodiscs as charge trapping centers for nonvolatile memory applications. Carbon, 2017, 113, pp.318 - 324. 10.1016/j.carbon.2016.11.063. hal-01428626

# HAL Id: hal-01428626 https://centralesupelec.hal.science/hal-01428626v1

Submitted on 16 Jul 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **Accepted Manuscript**

Integration of ammonia-plasma-functionalized graphene nanodiscs as charge trapping centers for nonvolatile memory applications

Jer-Chyi Wang, Kai-Ping Chang, Chih-Ting Lin, Ching-Yuan Su, Fethullah Güneş, Mohamed Boutchich, Chang-Hsiao Chen, Ching-Hsiang Chen, Ching-Shiun Chen, Lain-Jong Li, Chao-Sung Lai

PII: S0008-6223(16)31037-5

DOI: 10.1016/j.carbon.2016.11.063

Reference: CARBON 11502

To appear in: Carbon

Received Date: 7 October 2016

Revised Date: 21 November 2016 Accepted Date: 22 November 2016

Please cite this article as: J.-C. Wang, K.-P. Chang, C.-T. Lin, C.-Y. Su, F. Güneş, M. Boutchich, C.-H. Chen, C.-H. Chen, C.-S. Chen, L.-J. Li, C.-S. Lai, Integration of ammonia-plasma-functionalized graphene nanodiscs as charge trapping centers for nonvolatile memory applications, *Carbon* (2016), doi: 10.1016/j.carbon.2016.11.063.

This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting proof before it is published in its final form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

# Integration of ammonia-plasma-functionalized graphene nanodiscs as charge trapping centers for nonvolatile memory applications

Jer-Chyi Wang<sup>a,b,c,n</sup>, Kai-Ping Chang<sup>a</sup>, Chih-Ting Lin<sup>a</sup>, Ching-Yuan Su<sup>d</sup>, Fethullah Güneş<sup>e</sup>, Mohamed Boutchich<sup>f</sup>, Chang-Hsiao Chen<sup>g</sup>, Ching-Hsiang Chen<sup>h</sup>, Ching-Shiun Chen<sup>i</sup>, Lain-Jong Li<sup>j,k\*</sup>, Chao-Sung Lai<sup>a,c,l,m\*\*</sup>

<sup>a</sup>Department of Electronic Engineering, Chang Gung University, Guishan Dist. 33302, Taoyuan, Taiwan

<sup>b</sup>Department of Neurosurgery, Chang Gung Memorial Hospital, Guishan Dist. 33305, Taoyuan, Taiwan

<sup>c</sup>Center for Reliability Sciences & Technologies (CREST), Chang Gung University, Guishan Dist. 33302, Taoyuan, Taiwan

<sup>d</sup>Department of Mechanical Engineering, National Central University, Jhongli Dist. 32001, Taoyuan, Taiwan

<sup>e</sup>Department of Materials Science and Engineering, Izmir Kâtip Çelebi University, Cigli Main Campus, Izmir 35620, Turkey

<sup>f</sup>GeePs, CNRS UMR8507 Centrale Supelec, Univ Paris-Sud, Sorbonne Universités-UPMC Univ Paris 06, 11 Rue Joliot-Curie, Plateau de Moulon, Gif-sur-Yvette 91192, Cedex, France

<sup>g</sup>Department of Automatic Control Engineering, Feng Chia University, Seatwen Dist., Taichung 40724, Taiwan

1

<sup>h</sup>Sustainable Energy Development Center, National Taiwan University of Science and Technology, Taipei 10607, Taiwan

<sup>i</sup>Center for General Education, Chang Gung University, Guishan Dist. 33302, Taoyuan, Taiwan

<sup>j</sup>Institute of Atomic and Molecular Sciences, Academia Sinica, Taipei 10617, Taiwan

<sup>k</sup>Physical Sciences and Engineering Division, King Abdullah University of Science and Technology, Thuwal 23955-6900, Kingdom of Saudi Arabia

<sup>1</sup>Department of Nephrology, Chang Gung Memorial Hospital, Guishan Dist. 33305, Taoyuan, Taiwan

<sup>m</sup>Department of Materials Engineering, Ming Chi University of Technology, Taishan Dist. 24301, New Taipei City, Taiwan

<sup>n</sup>Department of Electronic Engineering, Ming Chi University of Technology, Taishan Dist. 24301, New Taipei City, Taiwan

<sup>\*</sup>Email: lance.li@kaust.edu.sa (L.J. Li)

<sup>\*\*</sup>Email: cslai@mail.cgu.edu.tw (C.S. Lai)

# **Abstract**

Graphene nanodiscs (GNDs), functionalized using NH<sub>3</sub> plasma, as charge trapping sites (CTSs) for non-volatile memory applications have been investigated in this study. The fabrication process relies on the patterning of Au nanoparticles (Au-NPs), whose thicknesses are tuned to adjust the GND density and size upon etching. A GND density as high as 8 × 10<sup>11</sup> cm<sup>-2</sup> and a diameter of approximately 20 nm are achieved. The functionalization of GNDs by NH<sub>3</sub> plasma creates N-H<sup>+</sup> functional groups that act as CTSs, as observed by Raman and Fourier transform infrared spectroscopy. This inherently enhances the density of CTSs in the GNDs, as a result, the memory window becomes more than 2.4 V and remains stable after 10<sup>4</sup> operating cycles. The charge loss is less than 10% for a 10-year data retention testing, making this low-temperature process suitable for low-cost non-volatile memory applications on flexible substrates.

# 1. Introduction

Two-dimensional (2D) materials, such as graphene, hexagonal boron nitride (h-BN), and transition metal dichalcogenides, have attracted significant attention because of their planar structure and outstanding properties [1-7]. Several studies have been performed for the integration of these materials in various applications such as field-effect transistors (FETs), heterojunctions, photo-detectors, supercapacitors, and conductive transparent electrodes [8-15]. With regard to graphene, its large-scale synthesis by chemical vapor deposition (CVD) and its transfer process onto functional substrates has opened up new opportunities for device integration. However, the growth as well as transfer of the material inherently generates structural and electrical defects. Although defects are usually detrimental for the operation of most devices, they can be used as trapping centers, i.e., charge storage nodes, for the fabrication of atomically thin-film non-volatile memories (NVMs) [16]. It has been demonstrated that both multi-layer graphene and functionalized graphene oxide (GO) exhibit a sufficiently large memory window, making these materials suitable for charge storage [17, 18]. This field of application is particularly important as the conventional floating gate (FG) flash memory suffers from severe scaling limitations and reliability issues, especially for the ultra-thin silicon dioxide tunneling layer [19, 20]. Industrial as well as academic researchers have investigated several alternatives to solve these limitations and issues over the last few years. One concept consists of replacing the FG with discrete charge storage nodes constructed from nanoparticles (NPs) such as Si, Ge, and Au [20-26] and charge trapping sites (CTSs) such as a silicon nitride layer [27-29]. It has been demonstrated that a large memory window can be obtained using the Ge-NPs embedded in dielectrics [20, 21]. Moreover, the spatial distribution of discrete charge

storage nodes prevents the lateral migration of charges and reduces the probability of leakage through tunnel and/or blocking oxides.

Several studies have demonstrated that nano-sized graphene structures, graphene nanodots, exhibit unique electronic properties on the edges, i.e., with zigzag and armchair structures [30-35], which are particularly favorable for functionalization. These graphenebased nanodots were patterned using either silica nanodots or polystyrene spheres as an etching mask | 36-38|. Although these methods produce organized graphene nanodot arrays, the tedious manufacturing procedure and the large diameter of the as-prepared nanodots (> 150 nm) limit their application in high-density memory devices. Yang et al. proposed the integration of isolated nanographene particles for charge trapping memory (CTM) [39]. However, the nanographene crystals were formed by remote plasma-enhanced chemical vapor deposition (RPECVD) and the overlap between the nanodots seriously affects the reliability of the device. In this study, we report on the self-aligned fabrication process of ultra-high density graphene nanodisc non-volatile memory (GND-NVM), where functionalized GNDs are used as CTSs. The memory characteristics are dependent on the size and thickness of the Au-NPs utilized to pattern the GND trapping nodes. The latter were functionalized using NH<sub>3</sub> plasma to introduce CTSs in the defects at the edges sites. This functionalization substantially enhances the memory window and the GND-NVMs exhibit a reliable endurance with an expected charge loss of 10% for 10-year data retention.

# 2. Experimental

# 2.1. Device fabrication

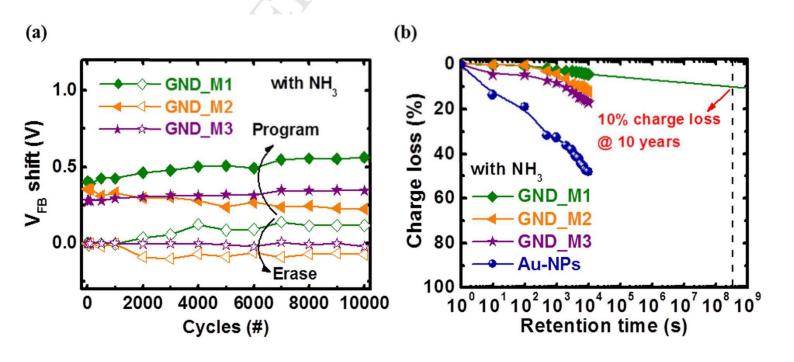

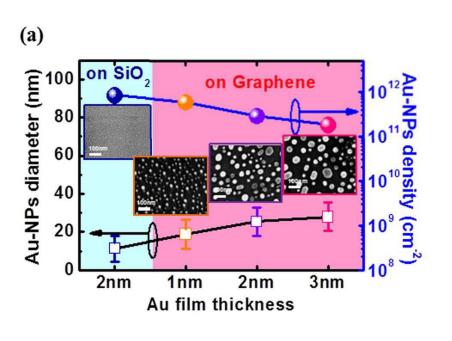

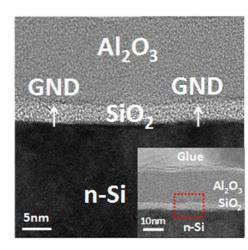

The GND-NVM devices have a (n)-c-Si/SiO<sub>2</sub>/GNDs/SiO<sub>2</sub>/Al structure. After substrate preparation using standard RCA cleaning, a 3-nm-thick tunnel oxide was thermally grown in a horizontal furnace at 850 °C under a N<sub>2</sub>/O<sub>2</sub> mixture. The uniformity of the tunnel oxide thickness is critical for ensuring that carrier injection from the n-type c-Si substrate to the GNDs occurs at the same speed. Then, the CVD graphene was transferred onto the 3-nmthick SiO<sub>2</sub> film as described by Suk et al. [40]. In this work, we employed Au-NPs as a hard mask to define the GNDs. In order to evaluate the impact of Au-NP thickness, 1-, 2-, and 3-nm-thick Au films were evaporated onto the CVD graphene and subjected to a rapid thermal annealing step at 700 °C for 30 s in N<sub>2</sub> atmosphere. The 1-, 2-, and 3-nm-thick Au samples are labeled as GND\_M1, GND\_M2, and GND\_M3, respectively. Fig. 1(a) displays the Au-NP diameter and density as a function of the Au thickness on CVD graphene, using SiO<sub>2</sub> as a reference. The density and size of the Au-NPs were analyzed by the contrast in color between the dark and bright parts using ImageJ software [41]. This yields GNDs with a diameter as small as 20 nm and a density of 8 × 10<sup>11</sup> cm<sup>-2</sup> for 1-nm thick Au film. Note that the density achieved here is comparable to the density of CTSs available in silicon nitride, for instance. Then, the GNDs were patterned by oxygen plasma using reactive ion etching (RIE) and the Au-NPs were stripped using potassium iodide (KI) etchant. Fig. 1(b) shows a high-resolution transmission electron microscopy (HRTEM) image of a GND enclosed between the tunnel oxide and an Al<sub>2</sub>O<sub>3</sub> film. The use of Al<sub>2</sub>O<sub>3</sub> film in HRTEM analysis is to clearly identify the interface that the GNDs can be observed. The atomic force microscopy (AFM) profile of GNDs after Au-NP stripping (for an initial Au film thickness of 3 nm) is displayed in Fig. S1 of the Supplementary Information. We

observed that the average width of the GNDs is close to 20 nm, as expected from the Au-NP diameter utilized and the height was an average of ~1 nm. Having defined the GNDs, it is now important to increase the density of the CTSs in order to trap the carriers injected from the substrate through the tunnel oxide during the program/erase (P/E) operations. For this, we functionalized the samples with low-power NH<sub>3</sub> plasma at 300 °C. All the samples were then capped with a 10-nm-thick SiO<sub>2</sub> film as a blocking oxide deposited by a plasma-enhanced CVD (PECVD) system. Finally, a 300-nm-thick Al film was evaporated and the gate was patterned by a photolithography process. Fig. 2 illustrates the entire fabrication process of the functionalized GND memory devices.

# 2.2. Material and electrical characterization

The scanning electron microscopy (SEM) images were acquired using a JEOL JSM-7500F apparatus. The AFM images were obtained using a Veeco Dimension-Icon system and measured at 0.976 Hz with 512 scanning lines. Further, Raman spectra were measured using an NT-MDT Raman microscopy system at 473 nm and a spot size of 3 µm. Before the measurement, the Si peak at 520 cm<sup>-1</sup> was used as a reference for calibration. Because of the small diameter of GNDs, ~20 nm, the Raman spectra of the GND samples were averaged. The Fourier transform infrared spectroscopy (FTIR) analyses were performed using a Bruker 66v/s system. The capacitance-voltage (C-V) characteristics were measured using an HP4284 precision LCR meter, and the gate pulse was generated using a HP8110A pulse generator. All the electrical measurements were performed under ambient conditions with a semi-auto cascade system.

# 3. Results and discussion

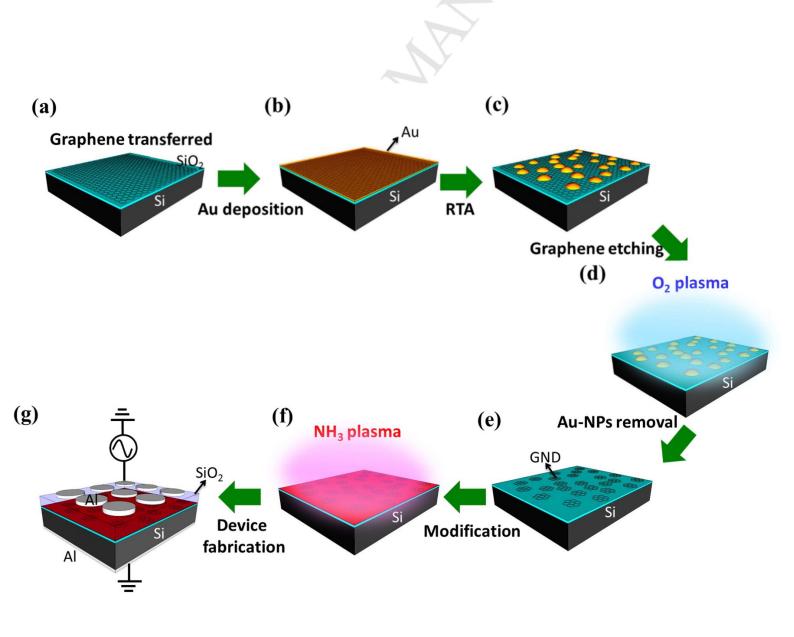

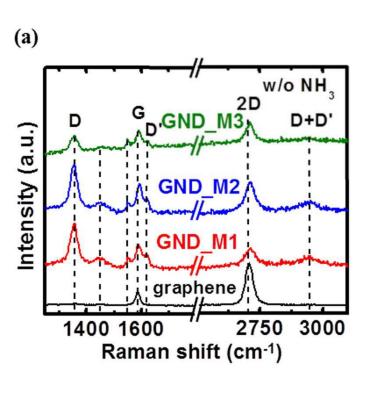

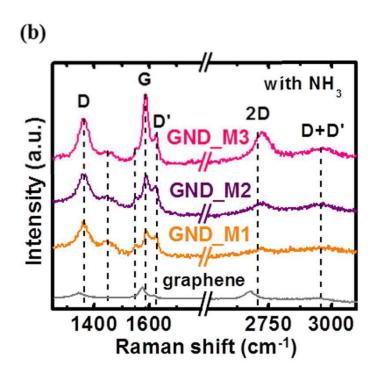

Fig. 3(a) shows the Raman spectra of pristine and GND samples before the NH<sub>3</sub> plasma functionalization. The pristine signature is typical for monolayer graphene with a 2D/G ratio close to 2.1. However, the GND signatures exhibit features that could be related to both doping and strain. First, we observe the D, D', and D+D' peaks, which can be assigned to defects created during the deposition and annealing of the Au hard mask. Moreover, we note the emergence of peaks at 1450 and 1550 cm<sup>-1</sup>. These contributions are stable and appear for both the treated and untreated samples. We believe that these peaks can be ascribed to the silicon substrate and the ambient, as reported by Spizzirri et al. [42]. Nevertheless, the blue shift observed for the G peak (from 1589 cm<sup>-1</sup> to 1596 cm<sup>-1</sup> for GND M3) and the 2D peaks (from 2706 cm<sup>-1</sup> to 2714 cm<sup>-1</sup> for GND M3) are contrary to those observed by Mohiuddin et al. [43]. They observed a G peak splitting when graphene is subjected to stress. Here, it is likely that despite the strain induced by the incorporation of Au from the hard mask, it is the doping inherent to these discs that is dominant, as we can see from the Raman shifts, i.e., p-type doping. Fig. 3(b) shows the Raman spectra for the same samples after NH<sub>3</sub> plasma exposure. The Raman shifts increase further to 1592 cm<sup>-1</sup> and 2729 cm<sup>-1</sup> for the G and 2D peaks of GND M3, respectively. The prominent D peak and the hardly distinguishable 2D peak for GND M1, GND M2, and the pristine sample indicate that the graphitic feature of the material is lost. GND M1 has the smallest diameter (< 20 nm), and it is possible that the NH<sub>3</sub> plasma functionalization has effectively transformed the material, as opposed to GND M3.

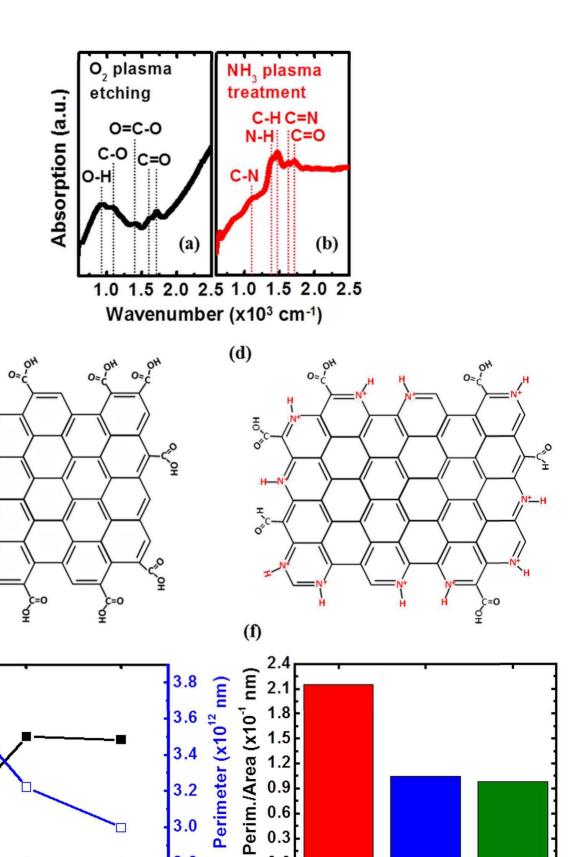

Fig. 4(a) presents the FTIR characterization of the GNDs after O<sub>2</sub> plasma etching. The oxygen functionalities appear at 1720 and 1627 cm<sup>-1</sup> (stretching vibrations from C=O), 1401 cm<sup>-1</sup> (carboxyl O=C-O), 1040 cm<sup>-1</sup> (C-O stretching vibrations), and 948 cm<sup>-1</sup> (O-H stretching vibrations). Fig. 4(c) illustrates the bonding of the O=C-O-H groups attached to the edges of the GNDs |44|. After the NH<sub>3</sub> plasma exposure, additional N groups appear at 1600 cm<sup>-1</sup> (C=N stretching vibrations), 1417 cm<sup>-1</sup> (N-H stretching), and 1080 cm<sup>-1</sup> (C-N stretching), as shown in Fig. 4(b). These observations confirm the incorporation of N into the lattice through the defect, and most likely at the edges of the GNDs. Fig. 4(d) illustrates the presence of the positively charged N-H<sup>+</sup> groups within the GNDs. These functional groups induced by the NH<sub>3</sub> plasma functionalization may substantially increase the amount of CTSs available for charge trapping. To further clarify the location of the functional groups within the GNDs, the peripheral and area values of the GNDs, according to the SEM images of Fig. 1(a), are shown in Fig. 4(e). In addition, the perimeter to area ratio of the GNDs is calculated and shown in Fig. 4(f). GND M1 exhibits the largest perimeter to area ratio, indicating that several functional groups are located at the edges of the GNDs for charge trapping. There is a blue shift of the G and 2D peaks, indicating that the p-type doping inherent to the Au-NPs has not been compensated by the n-type doping expected by the incorporation of N groups. This is advantageous for the operation of these memory devices, as the charges are trapped in deeper energy levels within the trapping medium, i.e., the GNDs, and as a result, encounters a larger energy barrier, improving the data retention behavior.

GND-NVMs were fabricated following the procedures depicted in Fig. 2. A control metal-oxide-silicon (MOS) capacitor without GNDs was also fabricated similarly. The

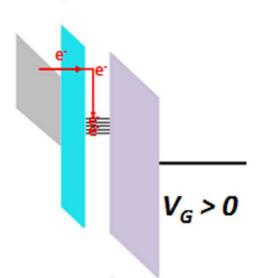

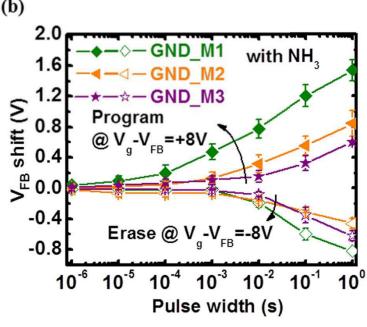

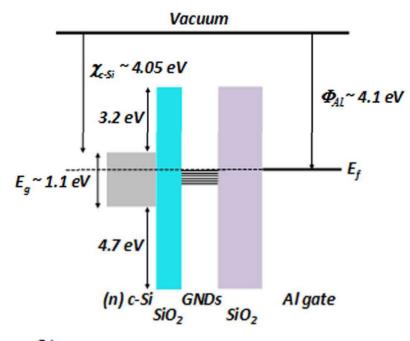

control MOS exhibits a negligible capacitance-voltage (C-V) hysteresis, i.e., a memory window, whereas a ~3 V window is clearly visible because of the larger amount of CTSs available in the functionalized GND devices, as shown in Fig. S2 of the Supplementary Information. Fig. 5 shows the program and erase (P/E) characteristics of the GND-NVMs with and without NH<sub>3</sub> plasma functionalization. Twenty samples were tested for each type of device. The flat-band energy diagrams as well as the P/E operations are illustrated in Fig. 6 for studying the operation mechanisms. During the program operation (Fig. 6(b)), the electrons tunnel through the 3-nm-thick SiO<sub>2</sub> barrier and fill the traps created in the GNDs, especially at the edges of the GNDs. Detailed illustrations are shown in Fig. S3 of the Supplementary Information. On the other hand, during the erase operation (Fig. 6(c)), the holes tunnel through the SiO<sub>2</sub> to recombine with the trapped electrons. This mechanism is identical to that observed in conventional CTS memories [45]. For the samples without NH<sub>3</sub> plasma functionalization (Fig. 5(a)), a flat-band voltage shift ( $\Delta V_{\rm FB}$ ) of approximately 0.5 V is observed for programming at  $V_{\rm g}$ - $V_{\rm FB}$  = 8 V for 1 s, and only 0.2 V at  $V_{\rm g}$ - $V_{\rm FB}$  = -8 V for 1 s for the erase operation. The small  $\Delta V_{\rm FB}$  obtained for these devices is inherent to the limited amount of CTSs in and surrounding the GNDs trapping medium. On the other hand, the characteristics are significantly improved when the GNDs are functionalized with NH<sub>3</sub> plasma, as depicted in Fig. 5(b). Indeed, at  $V_g$ - $V_{FB} = 8$  V and -8 V for 100 ms, one can achieve a  $\Delta V_{FB}$  of 1.2 V and -0.7 V for the P/E operations, respectively. This improvement is assigned to the larger amount of CTSs attached to the GNDs, as observed by FTIR (Fig. 4). Note that the erase operation is slower (i.e., the window is smaller for the same time) because of the larger effective mass of the hole and a larger energy barrier at the c-Si/SiO<sub>2</sub> interface encountered by the holes at ~4.7 eV, as opposed to the 3.2 eV for the electrons

[46]. Furthermore, in Fig. 5(b), even for the GND-NVMs with NH<sub>3</sub> plasma functionalization, a limited program and erase timing performances of 100 ms are observed. The insufficient operation speed can be ascribed to the small perimeter to area ratio of GNDs (< 0.215 nm), as shown in Fig. 4(f), by the hydrophobic nature of graphene surface for the Au-NP formation [47]. To enhance the program and erase characteristics, the optimization of GND size and density for a larger perimeter to area ratio could be performed by the modification of graphene surface to be more hydrophilic [47, 48].

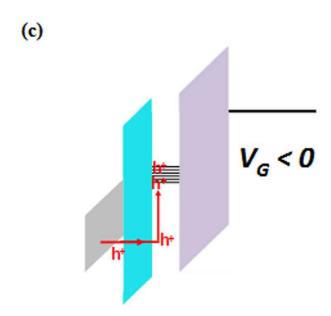

Fig. 7(a) shows the endurance characteristics of the GND-NVMs. All devices maintain the P/E operations without dramatic failure of the window up to  $10^4$  cycles, demonstrating that no charges are trapped elsewhere, other than in the GNDs. The GNDs act as isolated CTSs, and therefore, have a high immunity to tunnel or blocking oxide failure. Finally, we performed data retention measurements at room temperature. The devices are programmed at  $V_g$ - $V_{FB} = 8$  V to achieve a  $\Delta V_{FB}$  of 1 V. GND\_M1-NVM exhibits the best performance compared to the other devices, extrapolated to 10 years, as illustrated in Fig. 7(b). This implies that the thinner the hard mask, the better is the data retention. The higher CTS density of GND\_M1 compared to others is responsible for the superior memory properties, and the method developed in this work appears suitable for charge trapping NVM applications.

# 4. Conclusion

In this study, a charge trapping memory device based on the trapping of carriers in NH<sub>3</sub> plasma-functionalized graphene nanodiscs, with a diameter of 20 nm, was developed. The size and density of the GNDs can be tailored by tuning the Au-NP hard mask. The

incorporation of defect sites of the N-H<sup>+</sup> groups around the functionalized GNDs was identified using Raman and FTIR spectroscopy. As a result, data retention was improved because of the deep CTS level available for trapping electrons. The GND-NVMs with NH<sub>3</sub> plasma functionalization exhibit a wide memory window of 2.4 V, good endurance up to  $10^4$  cycles, and only a 10% charge loss at room temperature, extrapolated to 10 years. This method offers a low cost technology that can be integrated on flexible substrates.

# Acknowledgements

This research was supported by the Ministry of Science and Technology (MOST), R.O.C. under the Contract Nos. of MOST 103-2221-E-182-061-MY3, MOST 104-2221-E-182-041, MOST 104-2632-E-182-001, MOST 105-2628-E-182-001-MY3, and MOST 105-2632-E-182-001, and Chang Gung Memorial Hospital, R.O.C., under the Contract Nos. of CMRPD2D0072, CMRPD3D0112, CMRPD2E0031, CMRPD2F0121 and BMRPA74. MB and FG would like to thank the CNRS and the French Ministère des Affaires Etrangères et Européennes for their financial support through the ICT-ASIA programme (3226/DGM/ATT/RECH).

# References

- 1. A. K. Geim, Graphene: Status and prospects, Science 324 (2009) 1530–1534.

- 2. A. K. Geim, K. S. Novoselov, The rise of graphene, Nat. Mater. 6 (2007) 183–191.

- M. S. Fuhrer, C. N. Lau, A. H. MacDonald, Graphene: Materially better carbon, MRS Bulletin 35 (2010) 289–295.

- 4. D. Pacilé, J. C. Meyer, Ç. Ö. Girit, A. Zettl, The two-dimensional phase of boron nitride: Few-atomic-layer sheets and suspended membranes, Appl. Phys. Lett. 92 (2008) 133107.

- H. Wang, H. Yuan, S. Sae Hong, Y. Li, Y. Cui, Physical and chemical tuning of twodimensional transition metal dichalcogenides, Chem. Soc. Rev. 44 (2015) 2664–2690.

- 6. H. Oughaddou, H. Enriquez, M. R. Tchalala, H. Yildirim, A. J. Mayne, A. Bendounan, et al., Silicene, a promising new 2D material, Prog. Surf. Sci. 90 (2015) 46–83.

- M. Xu, T. Liang, M. Shi, H. Chen, Graphene-like two-dimensional materials, Chem. Rev. 113 (2013) 3766–3798.

- 8. F. Schwierz, Graphene transistors, Nat. Nanotechnol. 5 (2010) 487–496.

- A. D. Bartolomeo, Graphene Schottky diodes: An experimental review of the rectifying graphene/semiconductor heterojunction, Phys. Rep. 606 (2016) 1-58.

- P. Avouris, Graphene: Electronic and photonic properties and devices, Nano Lett. 10

(2010) 4285–4294.

- F. Bonaccorso, Z. Sun, T. Hasan, A. C. Ferrari, Graphene photonics and optoelectronics, Nat. Photonics 4 (2010) 611–622.

- J. S. Bunch, A. M. van der Zande, S. S. Verbridge, I. W. Frank, D. M. Tanenbaum, J. M. Parpia, et al., Electromechanical resonators from graphene sheets, Science 315 (2007) 490–493.

- C. Liu, Z. Yu, D. Neff, A. Zhamu, B. Z. Jang, Graphene-based supercapacitor with an ultrahigh energy density, Nano Lett. 10 (2010) 4863–4868.

- R. R. Nair, P. Blake, A. N. Grigorenko, K. S. Novoselov, T. J. Booth, T. Stauber, et al.,

Fine structure constant defines visual transparency of graphene, Science 320 (2008)

1308.

- M. D. Stoller, S. Park, Y. Zhu, J. An, R. S. Ruoff, Graphene-based ultracapacitors, Nano Lett. 8 (2008) 3498–3502.

- A. J. Hong, E. B. Song, H. S. Yu, M. J. Allen, J. Kim, J. D. Fowler, et al., Graphene flash memory, ACS nano 5 (2011) 7812–7817.

- S. Wang, J. Pu, D. S. H. Chan, B. J. Cho, K. P. Loh, Wide memory window in graphene oxide charge storage nodes, Appl. Phys. Lett. 96 (2010) 143109.

- A. Misra, H. Kalita, M. Waikar, A. Gour, M. Bhaisare, M. Khare, et al., Multilayer graphene as charge storage layer in floating gate flash memory, in Memory Workshop (IMW), 4th IEEE International (2012) 1-4.

- 19. A Fazio, Flash memory scaling, MRS Bull. 29 (2004) 814-817.

- M. Yang, T. P. Chen, Z. Liu, J. I. Wong, W. L. Zhang, S. Zhang, et al., Effect of annealing on charge transfer in Ge nanocrystal based nonvolatile memory structure, Appl. Phys. Lett. 106 (2009) 103701.

- C. Bonafos, M. Carrada, G. Benassayag, S. Schamm-Chardon, J. Groenen, V. Paillard, et al. Si and Ge nanocrystals for future memory devices, Mater. Sci. Semicond. Process. 15 (2012) 615-626.

- Y. Shi, K. Saito, H. Ishikuro, T. Hiramoto, Effects of traps on charge storage characteristics in metal-oxide semiconductor memory structures based on silicon nanocrystals, J. Appl. Phys. 84 (1998) 415.

- 23. W. R. Chen, T. C. Chang, P. T. Liu, P. S. Lin, C. H. Tu, C. Y. Chang, Formation of stacked nickel-silicide nanocrystals by using a co-mixed target for nonvolatile memory application, Appl. Phys. Lett. 90 (2007) 112108

- 24. J.S. Lee, Recent progress in gold nanoparticle-based non-volatile memory devices, Gold Bull. 43 (2010) 189–198.

- N. Goubet, J. Richardi, P. A. Albouy, M. P. Pileni, How to predict the growth mechanism of supracrystals from gold nanocrystals, J. Phys. Chem. Lett. 2 (2011) 417–422.

- J. Wang, X. Zou, X. Xiao, L. Xu, C. Wang, C. Jiang, et al., Floating gate memory-based monolayer MoS<sub>2</sub> transistor with metal nanocrystals embedded in the gate dielectrics, Small 11 (2015) 208-213.

- 27. H. A. R. Wegener, A. J. Lincoln, H. C. Pao, M. R. O. Connell, R. E. Oleksiak, H. Lawrence, The variable threshold transistor, a new electrically-alterable, non-destructive read-only storage device, IEEE International Electron Devices Meeting (1967) 70–73.

- 28. C. Y. Kang, Barrier engineering in metal-aluminum oxide-nitride-oxide-silicon (MANOS) flash memory: Invited, Curr. Appl. Phys. 10 (2010) e27-e31.

- 29. L. H. Ting, W. S. Yu, L. E. Kun, S. Y. Hao, L. S. Chih, Y. L. Wu, et al., BE-SONOS: A bandgap engineered SONOS with excellent performance and reliability, Technol. Digest-IEEE International Electron Devices Meeting (2005) 547–550.

- Y. W. Son, M. L. Cohen, S. G. Louie, Half-metallic graphene nanoribbons, Nature 444 (2006) 347–349.

- 31. J. Cai, P. Ruffieux, R. Jaafar, M. Bieri, T. Braun, S. Blankenburg, et al., Atomically precise bottom-up fabrication of graphene nanoribbons, Nature 466 (2010) 470–473.

- 32. M. Ezawa, Graphene nanoribbon and graphene nanodisk, Physica E: Low-dimensional Systems and Nanostructures 40 (2008) 1421–1423.

- V. Gupta, N. Chaudhary, R. Srivastava, G. D. Sharma, R. Bhardwaj, S. Chand,

Luminscent graphene quantum dots for organic photovoltaic devices,

J. Am. Chem. Soc. 133 (2011) 9960–9963.

- 34. M. W. Lee, J. Kim, J. S. Suh, Characteristics of graphene quantum dots determined by edge structures: three kinds of dots fabricated using thermal plasma jet, RSC Adv. 5 (2015) 67669-67675.

- 35. S. Bhandary, G. Penazzi, J. Fransson, T. Frauenheim, O. Eriksson, B. Sanyal, Controlling electronic structure and transport properties of zigzag graphene nanoribbons by edge functionalization with fluorine, J. Phys. Chem. C 119 (2015) 21227-21233.

- J. Lee, K. Kim, W. I. Park, B.-H. Kim, J. H. Park, T.-H. Kim, et al., Uniform graphene quantum dots patterned from self-assembled silica nanodots, Nano Lett. 12 (2012) 6078–6083.

- C. X. Cong, T. Yu, Z. H. Ni, L. Liu, Z. X. Shen, W. Huang, Fabrication of graphene nanodisk arrays using nanosphere lithography, J. Phys. Chem. C 113 (2009) 6529– 6532.

- 38. J. Peng, W. Gao, B. K. Gupta, Z. Liu, R. R. Aburto, L. Ge, et al., Graphene quantum dots derived from carbon fibers, Nano Lett. 12 (2012) 844–849.

- 39. R. Yang, C. Zhu, J. Meng, Z. Huo, M. Cheng, D. Liu, et al., Isolated nanographene crystals for nano-floating gate in charge trapping memory, Sci. Rep. 3 (2013) 2126.

- 40. J. W. Suk, A. Kitt, C. W. Magnuson, Y. Hao, S. Ahmed, J. An, et al., Transfer of CVD-grown monolayer graphene onto arbitrary substrates, ACS Nano 5 (2011) 6916-

6924.

- 41. M. D. Abràmoff, P. J. Magalhães, S. J. Ram, Image processing with ImageJ, Biophotonics international 11 (2004) 36–42.

- P. G. Spizzirri, Probe enhanced, nano-Raman spectroscopy (PERS); A sensitive technique for vibrational surface spectroscopy, Microscopy: Science, Technology, Applications and Education 2 (2015) 1389-1396.

- 43. T. M. G. Mohiuddin, A. Lombardo, R. R. Nair, A. Bonetti, G. Savini, R. Jalil, et al., Uniaxial strain in graphene by Raman spectroscopy: G peak splitting, Grüneisen parameters, and sample orientation, Phys. Rev. B 79 (2009) 205433.

- S. Kaniyankandy, S. N. Achary, S. Rawalekar, H. N. Ghosh, Ultrafast relaxation dynamics in graphene oxide: evidence of electron trapping, J. Phys. Chem. C115 (2011) 19110–19116.

- 45. E. Zhang, W. Wang, C. Zhang, Y. Jin, G. Zhu, Q. Sun, et al., Tunable charge-trap memory based on few-layer MoS<sub>2</sub>, ACS Nano 9 (2015) 612-619.

- A. D. Bartolomeo, H. Rücker, P. Schley, A. Fox, S. Lischke, K.-Y. Na, A single-poly EEPROM cell for embedded memory applications, Solid-State Electron. 53 (2009) 644-648.

- 47. C. J. Russo and L. A. Passmore, Controlling protein adsorption on graphene for cryo-EM using low energy hydrogen plasmas, Nat. Methods 11 (2014) 649–656.

- 48. N. Y. Garces, V. D. Wheeler and D. K. Gaskill, Graphene functionalization and seeding for dielectric deposition and device integration, J. Vac. Sci. Technol. B 30 (2012) 080301.

# **Figure Captions**

Fig. 1(Color online) (a) Au-NP dot density on silicon oxide and graphene layer as a function of the Au film thickness. The FE-SEM images of the Au-NPs are shown in inset figures. (b) Cross-sectional HRTEM image of GNDs on 3-nm  $SiO_2$  and capped with  $Al_2O_3$  to improve the contrast. The GNDs are  $\sim 20$  nm in diameter.

Fig. 2(Color online) Fabrication procedures of the GND-NVMs. (a) Graphene transferred on thermally grown 3-nm-thick SiO<sub>2</sub> tunneling oxide layer, (b) 1-, 2-, and 3-nm-thick gold films deposited on graphene layer by a thermal coater, (c) rapid thermal annealing (RTA) to form Au-NPs, (d) O<sub>2</sub> plasma to remove the unwanted graphene and form the graphene nanodiscs (GNDs), (e) Au-NPs stripped using gold etchant, potassium iodide (KI), (f) NH<sub>3</sub> plasma treatment to functionalize the GNDs, and (g) blocking oxide deposition and Al contact formation to fabricate GND-NVMs.

Fig. 3(Color online) Raman spectra of (a) pristine and (b) NH<sub>3</sub> plasma-functionalized graphene and GNDs as a function of the Au film thickness.

Fig. 4(Color online) FTIR spectra of GNDs after (a) O<sub>2</sub> plasma etching and (b) NH<sub>3</sub> plasma functionalization. The dominant functional groups of the GNDs without and with NH<sub>3</sub> plasma modification were O=C-O-H groups and N-H<sup>+</sup> groups respectively which may increase the CTSs for charge trapping, as illustrated in the chemical structure of the GNDs after (c) O<sub>2</sub> plasma etching and (d) NH<sub>3</sub> plasma functionalization respectively. (e) The peripheral and area dependence and (f) the perimeter to area ratio of GNDs as a function of the Au film thickness.

Fig. 5(Color online) (a) P/E characteristics of GND-NVMs without  $NH_3$  plasma functionalization. The gate voltage (calibrated by initial  $V_{FB}$ ) is 8 V for program and -8 V

for erase, with  $10^{-6}$  s to 1 s pulse width. (b) P/E characteristics of GND-NVMs with NH<sub>3</sub> plasma functionalization. The memory window enhances significantly.

Fig. 6(Color online) Illustration of the energy band diagram of (a) (n)-c-Si/SiO<sub>2</sub>/GNDs/SiO<sub>2</sub>/Al structure at the flat-band. (b) Program operation with the electrons tunneling through the 3-nm-thick SiO<sub>2</sub> barrier. (c) Erase operation with the holes tunneling through the 3-nm-thick SiO<sub>2</sub> barrier to recombine the trapped electrons.

Fig. 7(Color online) (a) Endurance characteristics of GND-NVMs with NH<sub>3</sub> plasma functionalization. The samples can sustain more than 10<sup>4</sup> cycles with +/-8 V/100 ms P/E operations. (b) Extrapolated data retention characteristics of GND-NVMs with NH<sub>3</sub> plasma functionalization. Less than 10 % charge loss after 10-year is expected.

(c)

P.

(e)

3.6

1.8

GND\_M1

GND\_M2

Area (x10<sup>13</sup> nm<sup>2</sup>) 8.1 8.2 8.2 8.1 8

2.8

GND\_M3

0.0

GND\_M1

GND\_M2

GND\_M3

(a)

**(b)**